Rambus Advances HBM2E Performance to 4.0 Gbps for AI/ML Training Applications

Highlights:

Fully-integrated HBM2E memory interface solution,consisting of verified PHY and controller,achieves industry's fastest performance

New benchmark in performance supportsaccelerators requiring terabyte-scale bandwidth for artificial intelligence/machine learning (AI/ML) training applications

Partners with SK hynix and Alchip to develop 2.5D HBM2E memory system solution using TSMC N7 process and CoWoS®advanced packaging technologies

Offers unrivaled system expertise supporting customers with interposer and package reference designs to speed time to market

SAN JOSE,California,Sept. 10,2020 -- Rambus Inc.(NASDAQ:RMBS),a premier silicon IP and chip provider making data faster and safer,today announced it has achieved a record 4 Gbps performance with the RambusHBM2E memory interface solutionconsisting of a fully-integrated PHY and controller. Paired with the industry's fastest HBM2E DRAM from SK hynix operating at 3.6 Gbps,the solution can deliver 460 GB/s of bandwidth from a single HBM2E device. This performance meets the terabyte-scale bandwidth needs of accelerators targeting the most demanding AI/ML training and high-performance computing (HPC) applications.

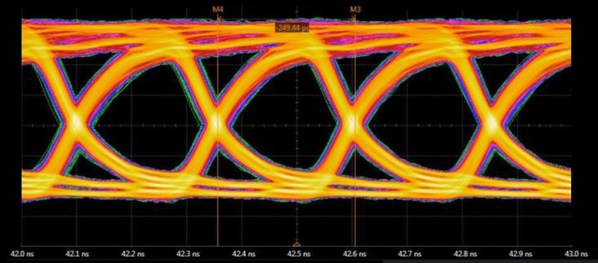

Rambus HBM2E Interface 4 Gbps Transmit Eye

"With this achievement by Rambus,designers of AI and HPC systems can now implement systems using the world's fastest HBM2E DRAM running at 3.6 Gbps from SK hynix," said Uksong Kang,vice president of product planning at SK hynix. "In July,we announced full-scale mass-production of HBM2E for state-of-the-art computing applications demanding the highest bandwidth available."

The fully-integrated,production-ready Rambus HBM2E memory subsystem runs at 4 Gbps without PHY voltage overdrive. Rambus teamed with SK hynix and Alchip to implement the HBM2E 2.5D system to validate in siliconthe Rambus HBM2E PHY and Memory Controller IP using TSMC's N7 process and CoWoS®(Chip-on-Wafer-on-Substrate) advanced packaging technologies. Co-designing with the engineering team from Rambus,Alchip led the interposer and package substrate design.

"This advancement of Rambus and its partners,using TSMC's advanced process and packaging technologies,is another important achievement of our ongoing collaboration with Rambus," said Suk Lee,senior director of the Design Infrastructure Management Division at TSMC. "We look forward to a continued partnership with Rambus to enable the highest performance in AI/ML and HPC applications."

"Alchip brought a demonstrated track record of success in 7nm and 2.5D package design to this initiative," said Johnny Shen,CEO of Alchip Technologies. "We're extremely proud of our contributions to Rambus' breakthrough achievement."

Rambus has 30 years of high-speed memory design applied to the most demanding computing applications. Its renowned signal integrity expertise was key to achieving an HBM2E memory interface capable of 4 Gbps operation. This raises a new benchmark for meeting the insatiable bandwidth requirements of AI/ML training.

"With silicon operation up to 4 Gbps,designers can future-proof their HBM2E implementations and can be confident of ample margin for 3.6 Gbps designs," said Matthew Jones,senior director and general manager of IP cores at Rambus. "As part of every customer engagement,Rambus provides reference designs for the 2.5D package and interposer to ensure first-time right implementations for mission-critical AI/ML designs."

Benefits of the Rambus HBM2E Memory Interface (PHY and Controller):

Achieves the industry's highest speed of 4 Gbps per pin,delivering a system bandwidth of 460 GB from a single 3.6 Gbps HBM2E DRAM 3D device.

Fully-integrated and verified HBM2E PHY and Controller reduces ASIC design complexity and speeds time to market

Includes 2.5D package and interposer reference design as part of IP license

Provides access to Rambus system and SI/PI experts helping ASIC designers to ensure maximum signal and power integrity for devices and systems

Features LabStation™ development environment that enables quick system bring-up,characterization and debug

Supports high-performance applications including state-of-the-art AI/ML training and high-performance computing (HPC) systems

For more information on the Rambus Interface IP,including our PHYs and Controllers,please visitrambus.com/interface-ip.

Follow Rambus:

Company website:rambus.com

Rambus blog:rambus.com/blog

Twitter:@rambusinc

LinkedIn:www.linkedin.com/company/rambus

Facebook:www.facebook.com/RambusInc

About Rambus Inc.

Rambus is a premier silicon IP and chip provider that makes data faster and safer. With 30 years of innovation,we continue to develop the foundational technology for all modern computing systems. Leveraging our semiconductor expertise,Rambus solutions speed performance,expand capacity and improve security for today's most demanding applications. From data center and edge to artificial intelligence and automotive,our interface and security IP,and memory interface chips enable SoC and system designers to deliver their vision of the future. For more information,visitrambus.com.

Press Contact:

Cori Pasinetti

Rambus Corporate Communications

t: (650) 309-6226

cpasinetti@rambus.com

Photo - http://cusmail.com/res/2023/07-23/22/67fe324efc3bfe4dd3cb4a14aeac557d.jpg

Logo - http://cusmail.com/res/2023/07-23/22/cf0bb325f4602e7a187eb6eb9322df11.jpg